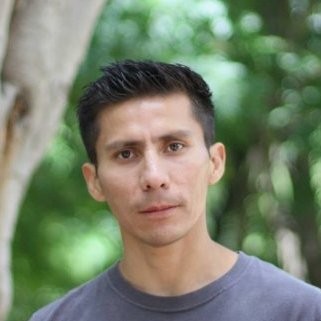

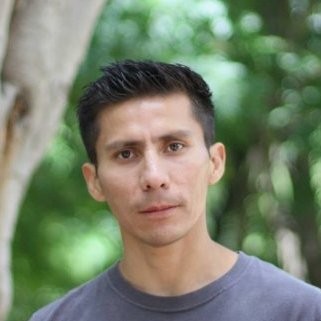

Marco Jacobo

Tell me more about Marco Jacobo?

Marco Jacobo is an experienced electrical engineer with 16.7 years of work experience. He has a strong background in systemverilog, data validation, and semiconductors. Marco has worked in various roles at Intel Corporation, including System Functional Validation Engineer and Cpld Code Developer for Complex PCB. He is skilled in programming, PCB design, and hardware architecture. Marco is also knowledgeable in testing, SOC, Verilog, and debugging. He is based in Guadalajara, Mexico.

For inquiries about Phone Number and Email, please click here Unlock Contact

Emails and Phone Numbers

About

Electrical enginner with MSc degree on telecommunication. Work mainly in the electronic industry as hardware design engineer, cpld-fpga code developer, shell and python scripting, and test content development in C. Familiar with test equipment like scope, TLA, multimeter, among others and mentorship to junior engineers.

Work Experience

system functional validation engineer at intel corporation

Cpld Code Developer For Complex Pcb

Semiconductor Manufacturing

Marco Jacobo's Professional Milestones

- Cpld Code Developer For Complex Pcb (2007-01-01~2011-01-01): Developed a high-quality code that met all client demands, ensuring flawlessly integrated PCB functionality.

- system functional validation engineer at intel corporation (2011-01-01~2016-08-01): Developed innovative system processes and improved product reliability through rigorous validation.

Skill

Systemverilog

Data Validation

Semiconductors

Programming

Pcb Design

Hardware Architecture

Electronics

Telecommunications

Testing

Soc

Verilog

Debugging

Hardware

Silicon

Rtl Design

Certification

Colleagues

Other Named Marco Jacobo

Frequently asked questions

We found 3 Marco Jacobo's email addresses

We found 3 Marco Jacobo's phone numbers

Marco Jacobo's social media include: Linkedin,

Marco Jacobo works for Intel Corporation

Marco Jacobo's role in Intel Corporation is system functional validation engineer at intel corporation

Marco Jacobo works in the industry of Semiconductor Manufacturing

Marco Jacobo's colleagues are Gustavo Gutierrez,Nitasha NS,User User

Marco Jacobo's latest job experience is system functional validation engineer at intel corporation at Intel Corporation